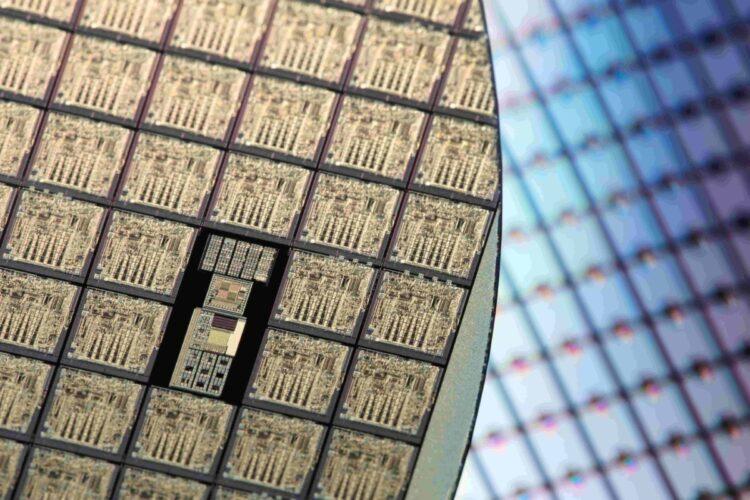

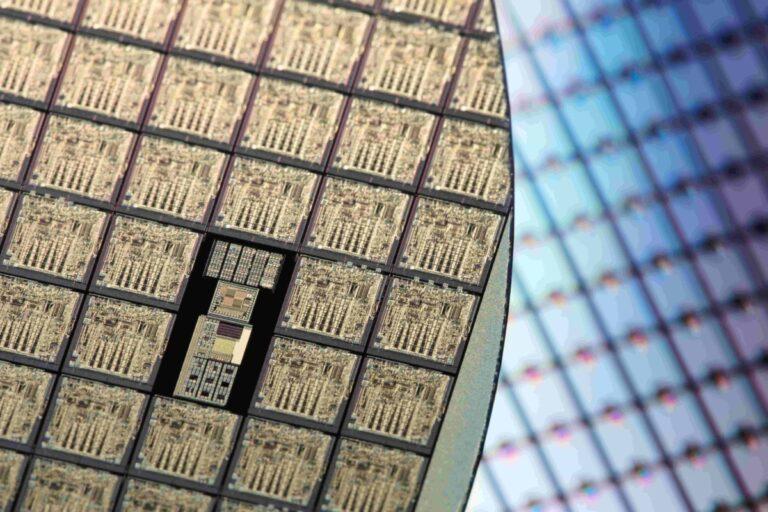

西門子數位化工業軟體日前宣佈與台積電深化合作,展開一系列新技術認證與協作,多項西門子 EDA 產品成功獲得台積電的最新製程技術認證。

台積電設計基礎架構管理部門負責人 Dan Kochpatcharin 表示:「台積電與包括西門子在内的設計生態系統夥伴攜手合作,為客戶提供經過驗證的設計解決方案,充分發揮台積電先進製程技術的強大效能和功耗優勢,幫助客戶持續實現技術創新。」

Calibre 獲得台積電的 N2 製程認證

用於積體電路(IC)驗證 sign–off的 Calibre® nmPlatform 工具已成功獲得台積電 N2 製程認證,可為早期採用台積電 N2 製程的廠商提供全面支援。獲得認證的 Calibre 工具包括 Calibre® nmDRC 軟體、Calibre® YieldEnhancer™ 軟體、Calibre® PERC™ 軟體和 Calibre® nmLVS 軟體。

台積電同時對用於電晶體層級電遷移(EM)與 IR 壓降(IR sign–off)的西門子 mPower™ 類比軟體進行 N4P 製程認證,雙方共同客戶現可以運用 mPower 獨有的 EM/IR sign–off 解決方案進行下一代的類比或射頻(RF)設計。

此外,台積電的 N4P、N3E 和 N2 客製化設計參考流程(CDRF),如今能和西門子的 Solido™ Design Environment 軟體搭配運作,在高 sigma 下進行進階變異感知驗證。為奈米級類比、RF、混合式訊號、記憶體和客製化數位電路提供電路驗證的西門子 Analog FastSPICE 平台,也已獲得台積電的 N5A、N3E 和 N2 先進製程認證。作爲台積電 N4P、N3E 和 N2 製程 CDRF 流程的一部分,Analog FastSPICE 平台現可支援台積電的可靠性感知模擬技術,解決 IC 老化和即時自體發熱效應,並提供其他進階的可靠性功能。

Aprisa 佈局與佈線解決方案獲得 N3 認證

西門子 Aprisa™ 佈局與佈線解決方案通過台積電 N3E 製程認證,進一步加強西門子在數位實施領域的投資承諾。Aprisa 提供業界領先的易用性,可幫助客戶更快遷移至 N3E 節點。

西門子數位化工業軟體 IC-EDA 執行副總裁 Joe Sawicki 表示:「台積電的創新速度令人驚嘆,我們很高興能與台積電建立長期的合作夥伴關係,針對台積電最新的製程持續最佳化我們的 EDA 解決方案,讓雙方共同客戶從中受益,滿足客戶快速變化的市場和業務需求。」

台積電認證西門子領先的 3D IC 解決方案

數款西門子 3D IC 解決方案也在台積電 3DFabric™ 技術認證方面取得進展。台積電已對 西門子 Calibre® 3DSTACK 軟體進行了 3Dblox 2.0 認證,用於實體分析與電路驗證,此認證包括支援小晶片間的 DRC 和 LVS 檢查,可滿足台積電 3DFabric 技術的相關要求。

此外,台積電還認證了一系列 Tessent™ 3D IC 解決方案,包括 Tessent 階層式 DFT、具有增強型 TAP(test access ports – 符合 IEEE 1838 標準)的 Tessent Multi-die,以及使用 Streaming Scan Network(SSN)和 IEEE 1687 IJTAG 網路技術的原生 FPP (Flexible parallel port)支援。雙方還按照台積電 3Dblox 標準投資構建 3D IC 測試生態系統,包括已知合格晶粒(KGD)迴路測試,以及利用 BMAP 及 PMAP 標準進行實體感知的晶粒間故障偵測與診斷。

-120x86.jpg)